芯片能做到1nm制程吗 芯片能做到多少纳米

2023-07-29 04:31 · 生活常识 · 潘冰蝶 · 【 字体:大 中 小 】

(文/程文智)三星电子今年7月25日在韩国京畿道华城园区V1生产线(EUV专用)为采用了新一代全环绕栅极(Gate All Around,简称GAA)晶体管制程节点的3nm芯片晶圆代工产品举行了出厂仪式。才过4个月不到,韩国媒体Naver就爆出,三星3nm制程的良率非常低,不足20%。而且其5nm和4nm节点的良率问题也迟迟没有得到改善。

其实,三星电子从2000年初就已经开始了对GAA晶体管结构的研究。自2017年开始,将其正式应用到3纳米工艺,并于今年6月宣布启动利用GAA技术的3纳米工艺的量产。是全球首家将GAA晶体管结构用于晶圆制造的代工企业。据悉,我国的一家矿机芯片企业PanSemi(磐矽半导体)是三星电子的第一家客户,目前也可能是其唯一的客户。

据报道,三星电子为了解决良率问题,找到了美国的Silicon Frontline Technology,向这家企业寻求帮助。据说目前进展情况还不错。

那么,三星电子在GAA上花的时间超过了20年,为何良率问题迟迟没有得到解决呢?问题究竟出在了哪里?我们先从芯片的最基础单元------晶体管结构的发展说起,然后看看有什么应对之策。

晶体管结构的发展历史

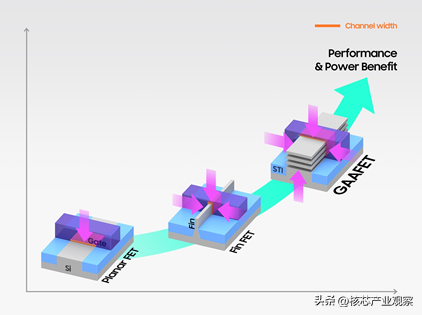

半导体芯片其实是众多晶体管(Transistor)的集合,而晶体管其实就是一个小的开关。一个晶体管就代表了一个0或者1,也就是所谓的一个位元。在20nm以上的制程中,使用的晶体管被称为金属氧化物半导体场效应管(MOSFET:Metal Oxide Semiconductor FET);20nm~3nm,采用的是鳍式场效应晶体管(Fin FET: Fin Field Effected Transistor);3nm以下,采用的则是全环绕栅极场效应晶体管(GAAFET:Gate All Around Field Effect Transistor)。

图:晶体管的结构发展(来源:三星)

为何会如此演进呢?主要是因为晶体管的工作原理,在晶体管内部,科学家定义了一个栅极长度(Gate Length)的概念,这是电子流通的方向,而其短边就是所谓的制程。

原理是在金属栅极上加一个电压来控制电子的导通和关闭。电子能够导通过去就代表1,如果关断则代表0。这个开关就是靠栅极施加电压来造成电场来控制的,可电场的主要影响在接触面上,如果栅极的长度越做越小,粉色的接触面积就会越来越小,当小到一个程度,要关住电子的时候,就会关不住。锁不住的电子就会偷偷溜过去。因此,先进制程中漏电流就会变大。

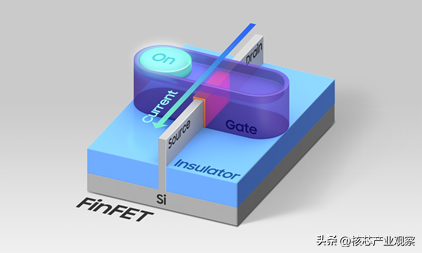

图:FinFET晶体管工作原理(来源:三星)

解决这个问题的办法就是增大栅极与电子通道的接触面积,接触面积越大,控制效果越好。所以到20nm以下就改用鳍式场效应晶体管,加电压的时候就变成粉色这部分面积就增加了,所以效果会比较好。电场的作用比较强,可以锁住电子不会漏电。

到了3nm以下,实在太小了,接触面积又不够了,怎么办呢?只好上下左右,统统把它包起来,用栅极把电子通道包起来,成为了GAAFET,这样的控制效果会比较好。

就目前来说,每一家晶圆代工厂大概都是用这样的方式去制作。

良率问题低迷该怎么办?

三星电子这次先于台积电推出3nm制程,但情况并没有好转,良率不足20%,这成本就有点高了。加上此前就由于在4nm和5nm制程良率无法得到改善,而让大客户高通和英伟达等大客户转单台积电了。此次要是还不能解决良率问题,可能大客户就此失去了。

为了能够更好地解决良率问题,三星电子此次找上了美国厂商Silicon Frontline Technology,让他们帮忙协助其提高3nm GAA结构的良率。

根据Silicon Frontline Technology官网信息,该公司位于加利福尼亚州圣何塞,主要提供半导体设计和验证解决方案。该公司为布局后验证提供有保证的准确和有保证的快速电阻、电容、ESD 和热分析,其产品已被70多家客户使用,其中包括全球前25家半导体供应商中的12家,得到领先代工厂的认可和使用,并已用于500多种设计中。而且,客户已经使用他们的技术解决了10nm、14nm、28nm、40nm、ADC、Serdes、敏感模拟电路、图像传感器、存储器、定制数字设计和电源设备的问题。

其主要的经验在于为晶圆厂提供静电放电(ESD)预防技术,而静电放电是晶圆生产过程中产生缺陷的主要原因,据悉也是三星3nm GAA技术的良率过低的重要原因之一。Silicon Frontline Technology公司已经藉由水质和静电放电(ESD)预防技术降低生产过程中的缺陷,以提高晶圆的生产良率。

虽然三星号称已经透过整合其合作伙伴使用的技术获得了积极成果,但实际成果还需要在未来几个月内持续观察。

据了解,目前市面上所做的失效分析中,90%以上的失效都是静电放电所造成的。根据电测结果,失效模式包含开路、短路或漏电、参数漂移、功能失效等。根据失效原因,失效模式可以分为电力过应、静电放电导致的失效、制造工艺不良导致的失效等。

静电放电是如何产生的呢?在芯片的制造过程中,半导体设备与芯片上的金属层之间,在制造过程中可能会发生静电放电。静电放电失效可以归结为两种情形,一是静电放电直接作用在了芯片上;二是静电放电干扰了生产的设备正常运行,或者是干扰了外部电路环境。

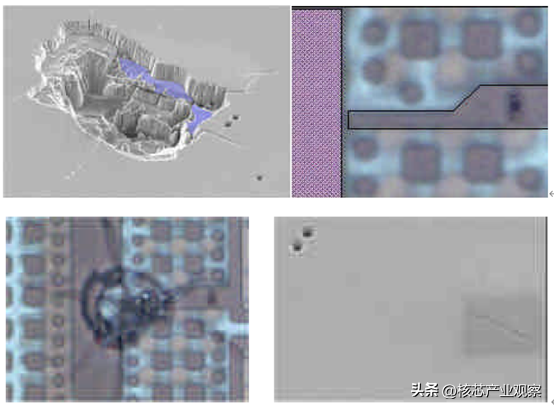

图:充电诱导损伤

上图就是所谓的充电诱导损伤(CID,Charging Induced Damage),就是当芯片在生产过程中,跟半导体设备接触或者接近,可能产生充电诱导损伤,这个图是晶圆表面被静电打坏的照片,仔细放大看,就会发现,实际上就是里面的某一个晶体管被损伤了,如果用显微镜仔细看,就会发现这颗IC基本上被打坏了。

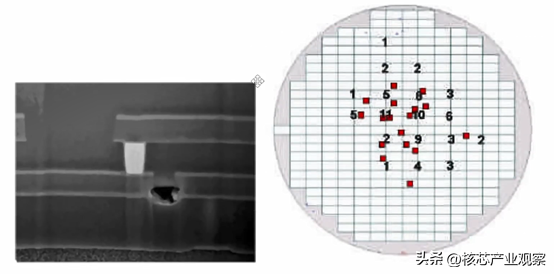

图:晶圆被静电打坏的剖面图

上图中左图表示的是一个被静电打坏的现象。从侧面看,你会发现,多层金属导线当发生静电打坏的现象,这个地方就会有缺陷,这时候,这颗芯片就坏掉了。通过分析可以发现在晶圆的某些位置,特别容易发生静电放电损坏芯片的现象。比入上图右图所示的红点,就是实验室中,科研人员测得的在某个条件下,某些位置容易打伤芯片。

结语

三星遇到的一直都是良率的问题,所以这次,他们想通过Silicon Frontline Technology提供的静电放电模拟软件协助其找到原因,进而解决良率的问题。如果此次他们能够成功解决良率问题,那么在未来的先进制程竞争中超越台积电。

毕竟台积电目前的3nm制程采用的仍然是FinFET技术,到2025年2nm时,他们才会采用GAAFET技术。而三星此次如果解决了良率问题,那么在2nm竞争时,将会比台积电多出3年的实践经验。因此,两家公司的决战点应该会在2025年之后。

免责声明:本文仅代表文章作者的个人观点,与本站无关。其原创性、真实性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容文字的真实性、完整性和原创性本站不作任何保证或承诺,请读者仅作参考,并自行核实相关内容。

猜你喜欢

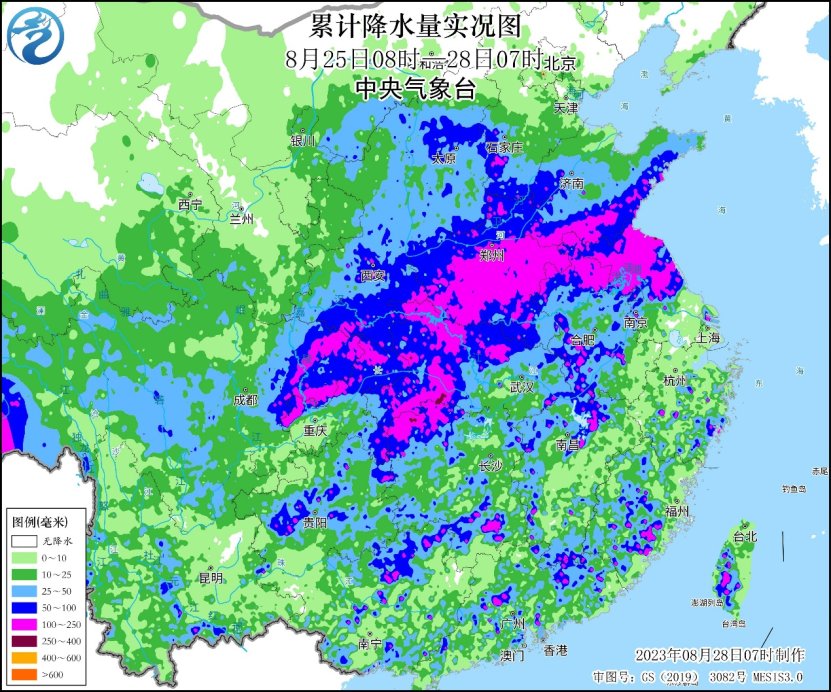

涿州市有雨吗 河北涿州下雨了吗

140

140

中央气象台8月17日10时发布强对流天气蓝色预警

766

766

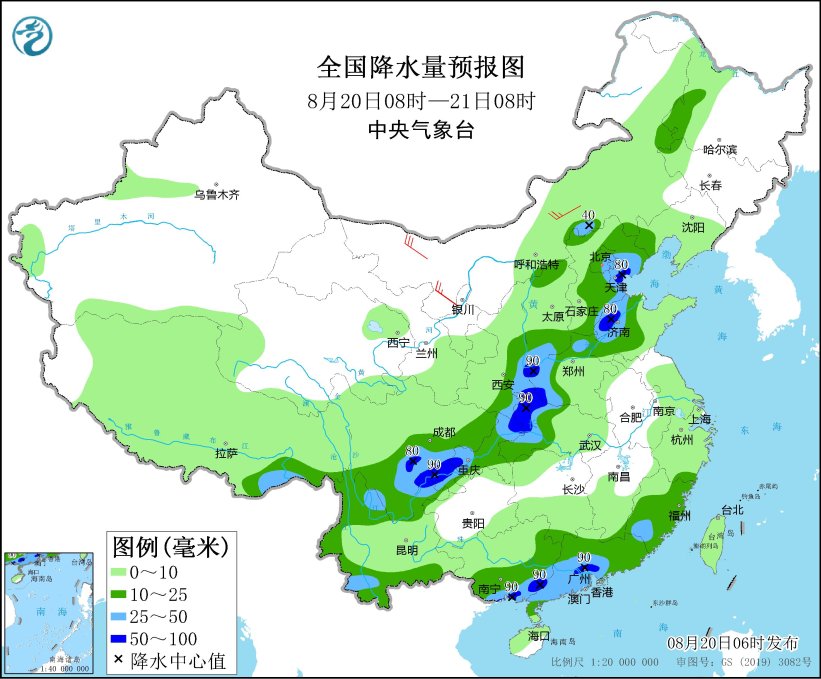

中央气象台8月20日06时发布暴雨蓝色预警

654

654

读绘本的技巧与方法 读绘本的技巧是什么

141

141

福建金门供水工程中标单位 福建 金门 供水

204

204

枭龙越野车油耗高吗 枭龙越野车是什么牌子

131

131

弱冷空气影响北方 长江中下游地区和贵州多降雨

674

674

《恶魔的小叔宠妻小说》免费完结,超级好看!

110

110

反诈工作格局 反诈宣传防范工作

85

85

广东省茂名市气象台发布雷雨大风黄色预警信号

854

854

春季有哪些养生美食

白俄罗斯的货币叫什么

五院四系是哪些学校

淋漓尽致的意思是什么

文景小学怎么样

商品生产日期喷码怎么看

横刀立马是什么意思

热干面调料有哪些

竞聘演讲稿结束语怎么写

“世界大同”是什么意思